|

AT9535

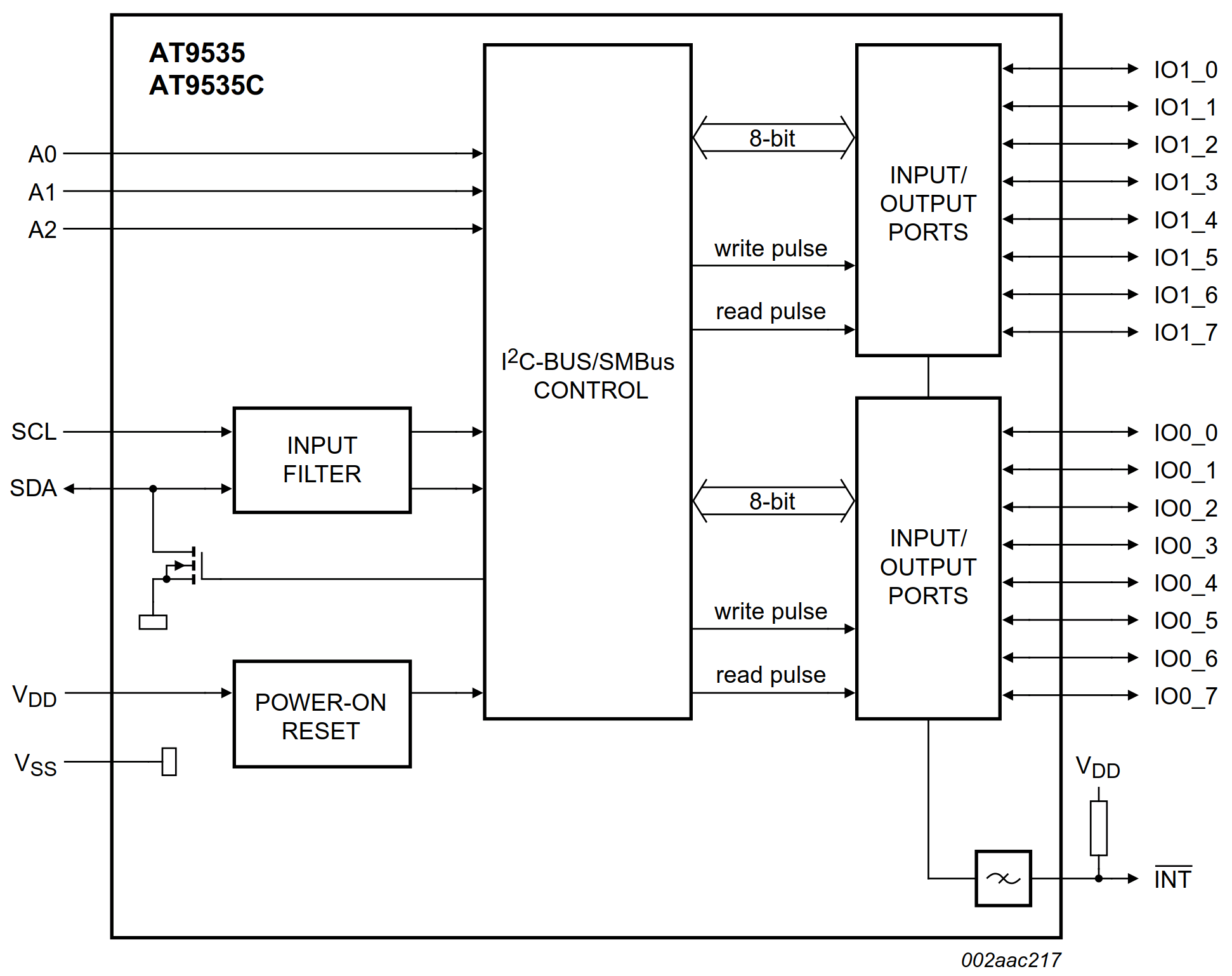

Description The AT9535 and AT9535C are 24-pin CMOS devices that provide 16 bits of General Purpose parallel Input/Output (GPIO) expansion for I2C-bus/SMBus applications. The improvements include higher drive capability, 5V I/O tolerance, lower supply current,individual I/O configuration, and smaller packaging. I/O expanders provide a simple solution when additional I/O is needed for ACPI power switches, sensors, push buttons,LEDs, fans, etc. The AT9535 and AT9535C consist of two 8-bit Configuration (Input or Output selection), Input, Output and Polarity Inversion (active HIGH or active LOW operation)registers. The system master can enable the I/Os as either inputs or outputs by writing to the I/O configuration bits. The data for each input or output is kept in the corresponding Input or Output register. The polarity of the read register can be inverted with the Polarity Inversion register. All registers can be read by the system master. Although pin-to-pin and I2C-bus address compatible with the AT8575, software changes are required due to the enhancements. The AT9535 is identical to the AT9555 except for the removal of the internal I/O pull-up resistor which greatly reduces power consumption when the I/Os are held LOW. The AT9535C is identical to the AT9535 except that all the I/O pins are high-impedance open-drain outputs. The AT9535 and AT9535C open-drain interrupt output is activated when any input state differs from its corresponding Input Port register state and is used to indicate to the system master that an input state has changed. The power-on reset sets the registers to their default values and initializes the device state machine. Three hardware pins (A0, A1, A2) vary the fixed l2C-bus address and allow up to eight devices to share the same 12C-bus/SMBus. The fixed 12C-bus address of the AT9535and AT9535C are the same as the AT9555 allowing up to eight of these devices in any combination to share the same I2C-bus/SMBus. Features

Typical Application

|