|

AT9557

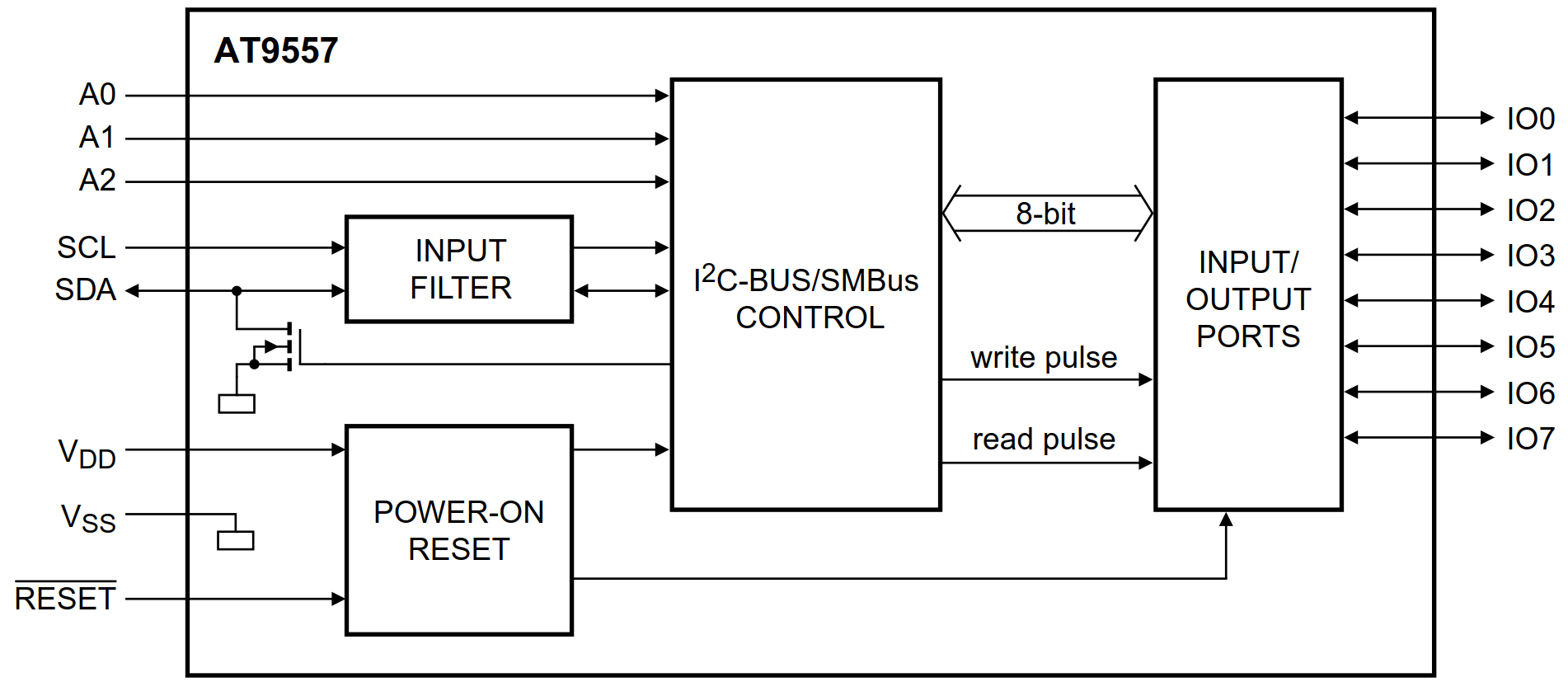

description TheAT9557 is a silicon CMOS circuit which provides parallel input/output expansion for SMBus and I2C- bus applications. The AT9557 consists of an 8-bit input port register, 8-bit output port register, and an I2C-bus/SMBus interface. It has low current consumption and a high-impedance open-drain output pin, IO0. The system master can enable the AT9557’s I/O as either input or output by writing to the configuration register. The system master can also invert the AT9557 inputs by writing to the active HIGH polarity inversion register. Finally, the system master can reset the AT9557 in the event of a time-out by asserting a LOW in the reset input. The power-on reset puts the registe rs in the ir default state and initializes the I2C-bus/SMBus state machine. The RESET pin causes the same reset/initialization to occur without de-powering the part. Features Lower voltage, higher performance migration path for theAT9557 8 general purpose input/output expander/collector Input/output configuration register Active HIGH polarity inversion register I2C-bus and SMBus interface logic Internal power-on reset Noise filter on SCL/SDA inputs Active LOW reset input 3 address pins allowing up to 8 devices on the I2C-bus/SMBus High-impedance open-drain on IO0 No glitch on power-up Power-up with all channels configured as inputs Low standby current Operating power supply voltage range of 2.3 V to 5.5 V 5V tolerant inputs/outputs 0 kHz to 400 kHz clock frequency ESD protection exceeds 2000 V HBM per JESD22-A114 and 1000 V CDM per JESD22-C101 Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA Three packages offered: SO16, TSSOP16, HVQFN16 diagram

|